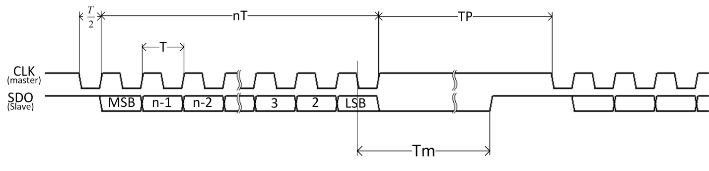

SSI (Synchronous Serial Interface) is a synchronous, point-to- point, serial communication channel for digital data transmission. A common clock signal is used on the receiving and sending side.

SSI has a high protocol efficiency and can be implemented over various hardware platforms, making it very popular among sensor manufacturers.

This code module is designed for different packet transmission frequencies and is also available in both I/O module families: configurable I/O modules used to configure I/O and protocol functionalities for a given code module delivered as part of a Custom Implementation Package; and Simulink®-programmable FPGA I/O modules optimized for use with the MathWorks® HDL Coder™ toolbox.

Three Code Modules are available:

- SSI Master

- SSI Slave

- SSI Sniffer

Common Applications

- Interface to standalone absolute encoders

- Ideal for applications that must be reliable and robust, for example in industrial environments

- Motor control for feedback loop

- Industrial machinery position control

- Various control applications with absolute position feedback